# Wafer characterization tests MAIA BEE project

Overview

Wafer characterization

Sensor test

In situ debug and maintenance DAQ

LPC LAL LLR

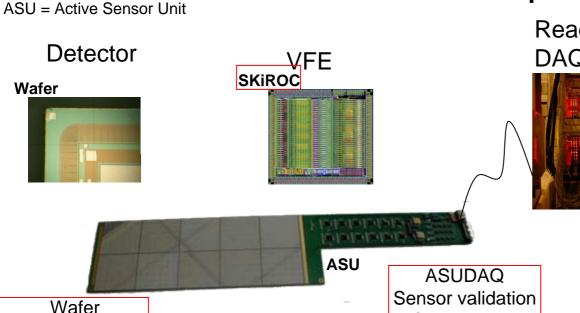

### Instrumental chain ongoing work at LPC from Wafer to data acquisition

Read-out DAQ

first developments of a generic design

Test bench

Analysis Software

econstruction SW

**ISDDAQ** Debug, Monitoring Maintainance

ISDDAQ architecture issue

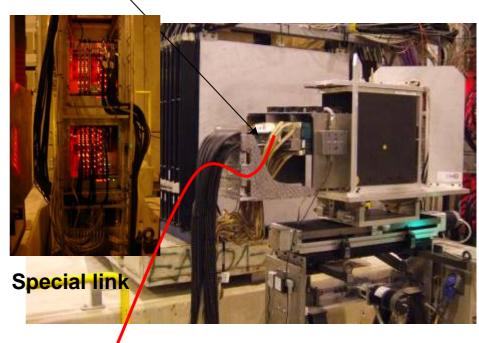

On beam integration

Architecture level R&D

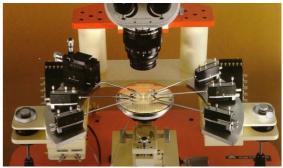

### Wafer test bench being set up

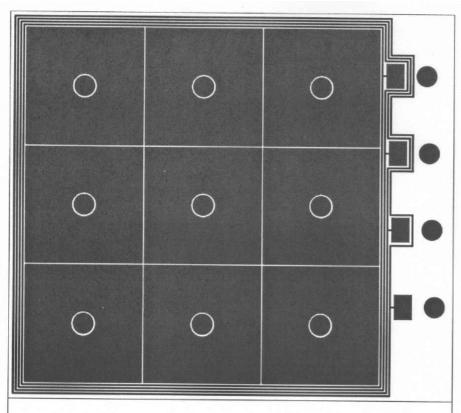

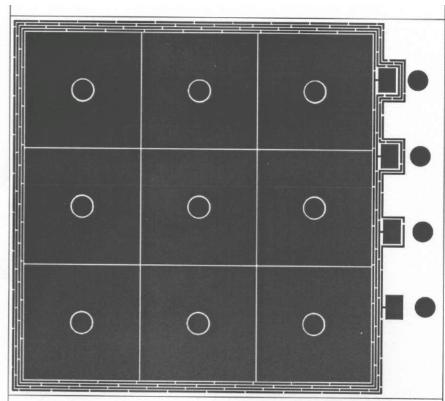

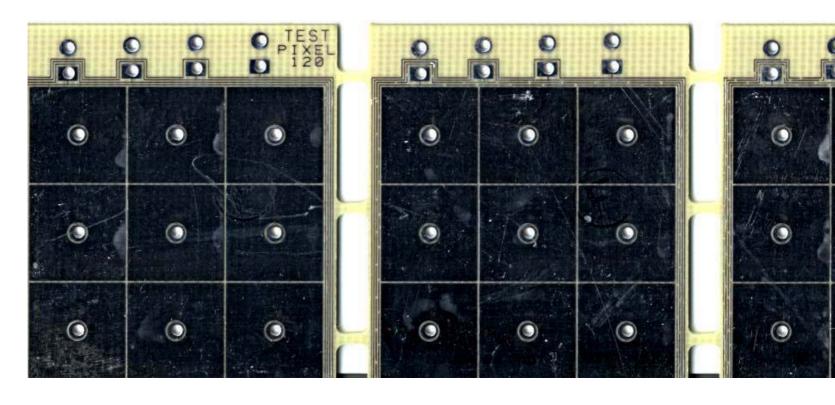

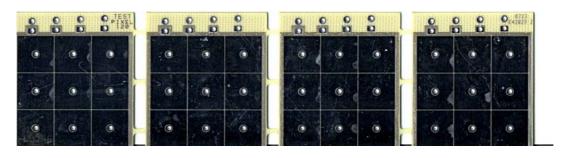

- 3x3 Test wafers specifications

- Probe tips test apparatus

- Silicon simulation tools

### **Towards EUDET.**

Validation & Test of the whole chain

Cosmic tests

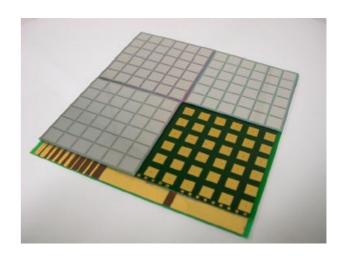

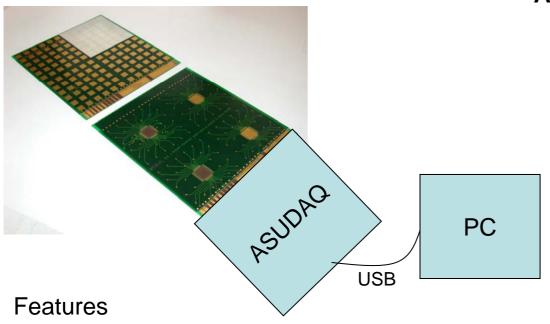

**ASUDAQ** prototype

- R&D test tools for sensor and electronics

- Validation, debugging and maintenance on beam

Crosstalk studies

Design validation

## Wafer

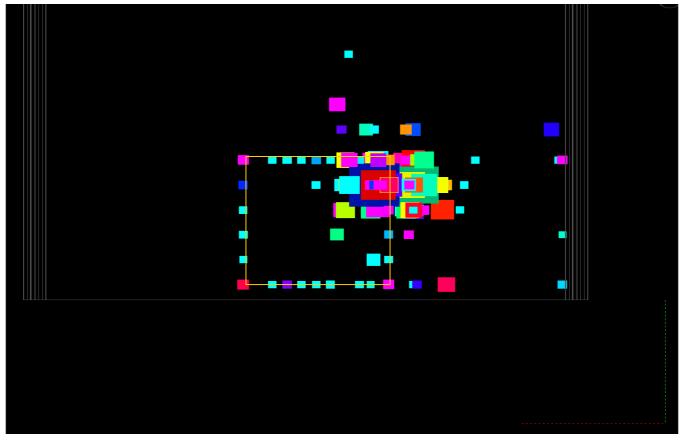

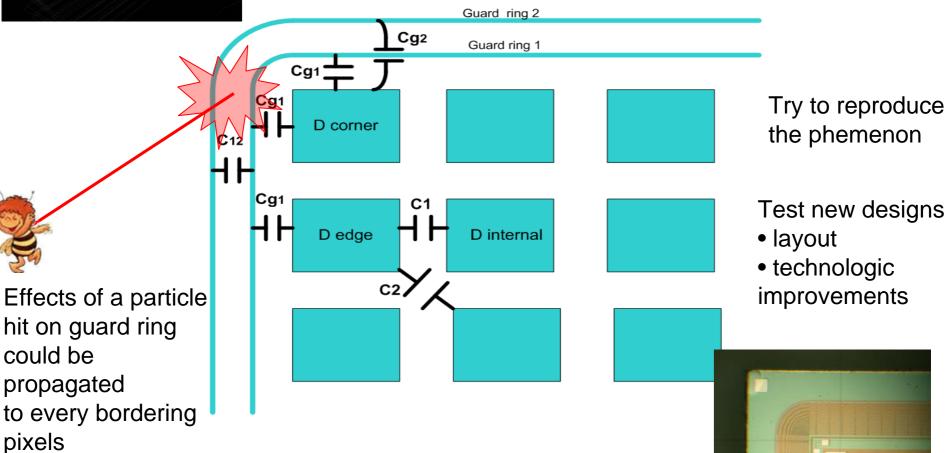

Unexpected behavior seen during test beam : SQUARE events ! Unmatched pattern according to physics models... Has to be understood and solved

### Wafer

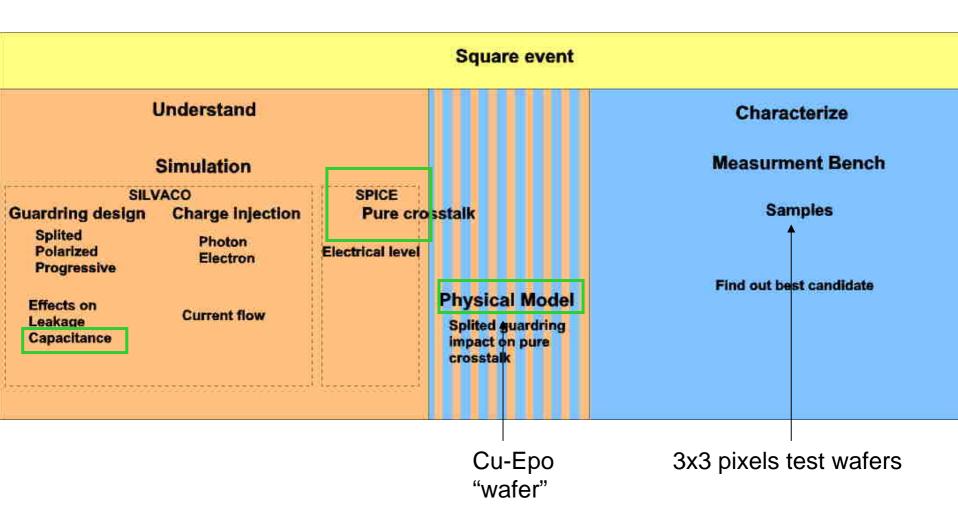

Understand Square events origins Crosstalk studies according to design options

4

Various 3x3 test wafer to be produced by OnSemi

As result, select the best design technique...

## Wafers: Method

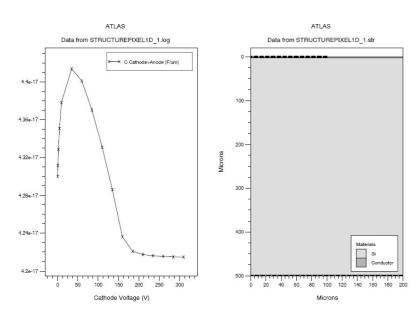

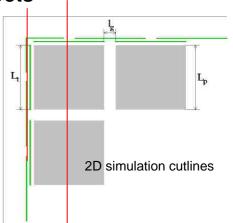

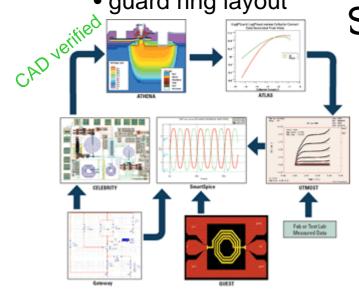

## SILVACO SIMULATIONS

C(V) between pixel and common bias and C(V,f,a,b,c,d...)

First step to verify capacitance values between pixels, guardrings, substrate

Then back annotate to SPICE simulation

Simulated Cap. Values are within a 20% range from expected values calculated with first order formula

3D simulation are ongoing to take into account border effects

Second step to simulate ionization effects (electron or photon) or SEE/SEU events

Third step (following months) to evaluate design parameters impact on C and explore new designs of guardrings from crosstalk point of view

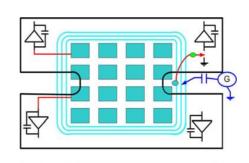

# Segmented guardring technique may prevent Xtalk by a factor 3

diaphonie pixel – 3x3 matrix

Cgb = 4 pF Cgg=24pF Cpg = 1 pF

SPICE

|     | Plain guardring |     |     |     |     |  |  |

|-----|-----------------|-----|-----|-----|-----|--|--|

| 5.6 |                 |     | 5.6 |     | 5.6 |  |  |

|     |                 |     |     |     |     |  |  |

|     |                 | 1   | 100 | 1   |     |  |  |

|     |                 |     |     |     |     |  |  |

| 5.6 |                 | 0.3 |     | 0.3 | 5.6 |  |  |

|     |                 |     |     |     |     |  |  |

|     |                 | 0.5 | 0.3 | 0.5 |     |  |  |

|     |                 |     |     |     |     |  |  |

| 5.6 |                 |     | 5.6 |     | 5.6 |  |  |

|     |                 |     |     |     |     |  |  |

| Guardring | non segme | enté, Signal | l at G1 |  |

|-----------|-----------|--------------|---------|--|

|           |           | 100          |         |  |

|           | 20        | 5.6          | 20      |  |

|           |           |              |         |  |

|           | 5.6       | -            | 5.6     |  |

|           | 20        | 5.6          | 20      |  |

|           |           |              |         |  |

| Segmented guardring 160 fF |      |      |      |   |

|----------------------------|------|------|------|---|

| 2                          |      | 42   |      | 2 |

|                            |      |      |      |   |

|                            | 0.3  | 100  | 0.3  |   |

|                            |      |      |      |   |

| 2                          | 0.1  | -    | 0.1  | 2 |

|                            | 0.15 | 0.08 | 0.15 |   |

|                            |      |      |      |   |

| 2                          |      | 2    |      | 2 |

|                            |      |      |      |   |

|   | g 1 segment<br>=160 fF | té, Signal at G1_2 segment, |     |   |

|---|------------------------|-----------------------------|-----|---|

| 6 |                        | 100                         |     | 6 |

|   | 1                      | 5.6                         | 1   |   |

| 4 | 0.2                    | -                           | 0.2 | 4 |

|   | 0.4                    | 0.2                         | 0.4 |   |

| 4 |                        | 4                           |     | 4 |

# Physical Model: Cu-Epoxy

- Study pure crosstalk effects (various configurations)

- Measurement method validation

- Test bench calibration

### Splited guardring

- •4 @ 1 cm

- •4 @ 3 mm

- •2 @ 1 cm + 2 unsplited

# Physical Model: Cu-Epoxy

### **Simulation**

capacitive coupling

guard ring layout

Wafer Setup and tools

PCB for test electronics

Supporting PCB

Wafer

XYZ table

### Characterization

- Charge injection

- pixel signal analysis

### **Test bench**

- pulse generator

- micropositioner & probes

- shaper + scope

I(V) / C(V

10

CALICE - 12/07/07 - Rémi CORNAT (LPC)

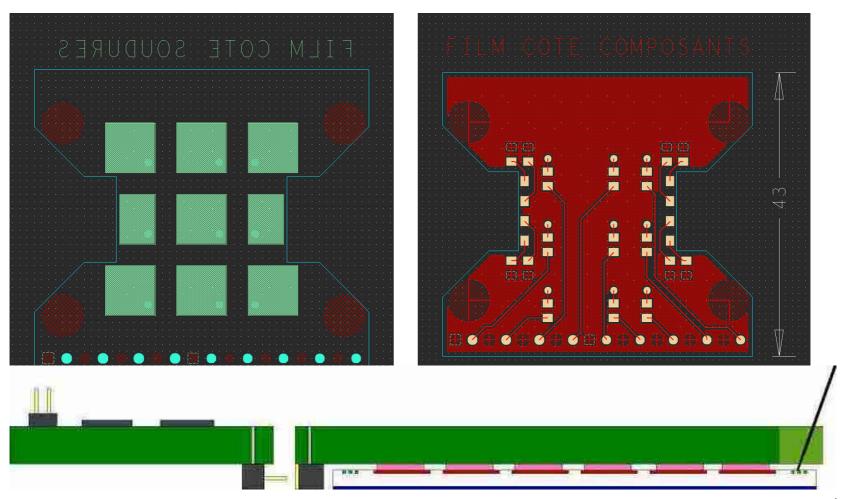

# PCB to glue 3x3 test wafers

Sent to fab. Last week

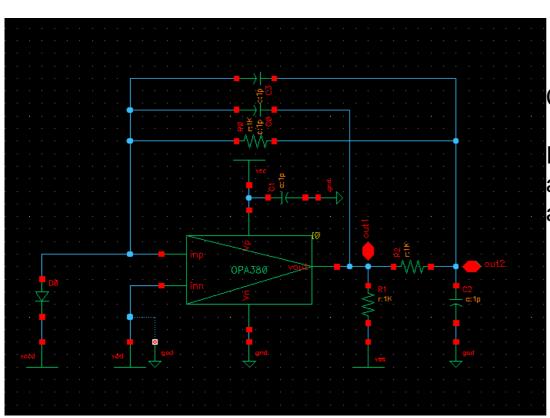

## Instrumentation board

Sent to fab. Last week

Compatible with wafer gluing PCB

Includes 3 OPA for signal shaping and transimpedance adaptation to a scope

Nice picture of the board here

**OPA380 or OPA657**

= done or good results

Wafer actions

#### Simulation

- Software know-how & test case (first try on 10th of april)

- Simulate: depletion area between segments, polarization effects, photon or electron effects, capacitance extraction, multiple pixels and guardring, 3D

- Comparison with test beam data (may validate "pure crosstalk" hypothesis)

### Physical Model

- Layout

- Simulations (Spectraa, spice)

- Bench tests during July

- Measurement bench

- Assembly (black box, Keithley,...)

- Test board design

- Connector

- Charge injector

- Shaper

- 3x3 matrix specifications

- · Back from fab. on oct/nov

- Measurements will follow

- Interaction with manufacturer

- Layout options

- Common wafer floorplan

### Part II

# MAIA BEE

M aintenance

A pparatus

I ncluding (data)

A cquisition (on)

B eam (for)

E UDET

E CAL

{ASUDAQ, ISDDAQ} = MAIA BEE

ASUDAQ = ASU DAQ

ASUDAQ = In Situ Debug DAQ (of one SLAB)

## **ASUDAQ**

### Cosmic test of ASU

Active Sensor Unit

**Cosmic test bench** for ASU characterization.

First R&D step towards EUDET production tests

- full **slow control** including internal probing system control

- access to analog test points (embedded ADC)

- read out of 4 SKiROC through USB & PC

- cosmic bench environment support (triggers)

- mechanical jaw providing damageless contacts to ASU

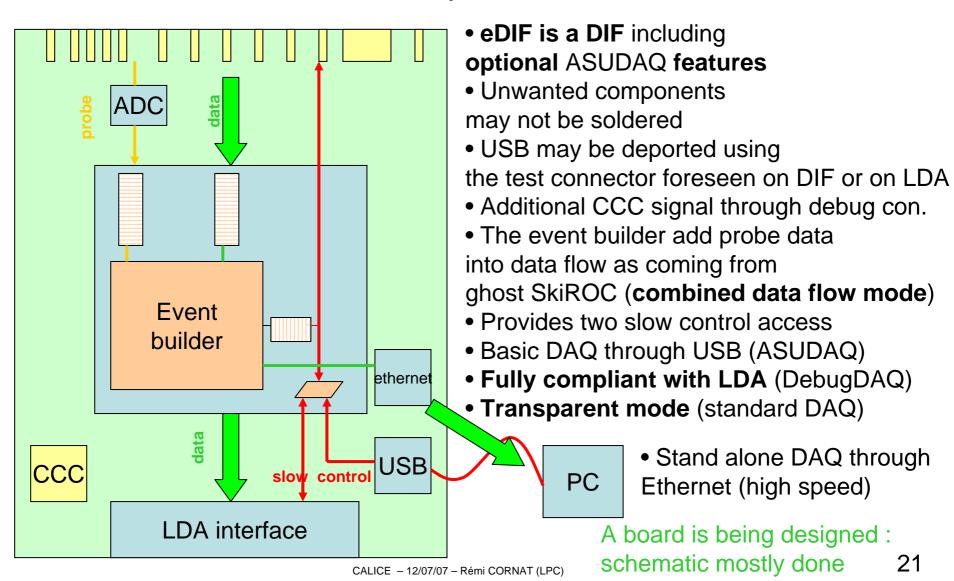

A board is being designed : schematic mostly done

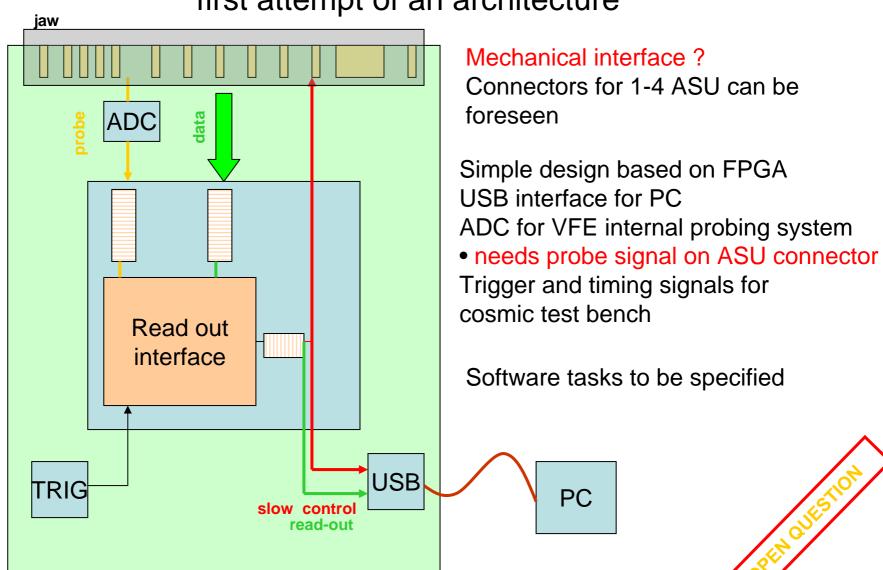

### **ASUDAQ**

### first attempt of an architecture

#### ASU/SLAB connector I/O LPC 22/06/07

|          |                   |          |     | _         |

|----------|-------------------|----------|-----|-----------|

| CAT      | NAME              |          |     |           |

| HV       |                   |          |     |           |

|          |                   |          |     |           |

| POWER    | GND               |          | 1   |           |

|          | 3.3V              |          | 1   |           |

|          |                   |          |     |           |

| BIAS     |                   |          | 0   |           |

|          |                   |          |     |           |

| REFERENC | E                 |          | 0   |           |

|          |                   |          |     |           |

| ccc      | clkp 40MHz        | 1 LVDS   | 0   |           |

|          | clkn 40MHz        |          |     |           |

|          | Reset             | 1 OC     | oc  |           |

|          | power_on_xxxx     | 5 LVTTL  | 0   | new 22/06 |

|          | testin            | analogue | 0   | new 22/06 |

| sc       | clk_sc            | 1 LVTTL  | 0   |           |

|          | rstb sc           | 1 LVTTL  | 0   |           |

|          | sroutscbuf        | 1 LVTTL  | ı   |           |

|          | srin_sc           | 1 LVTTL  | 0   |           |

| PROBE    | analogue_probe    | analogue | Ain |           |

|          | digital_probe     | 1 LVTTL  | I   |           |

|          |                   |          |     |           |

| READOUT  | clkp_5MHz / 1 MHz | 1 LVDS   | 0   |           |

|          | clkn_5MHz / 1 MHz |          |     |           |

|          | StartAcq          | 1 LVTTL  | 0   |           |

|          | ValEvtp           | 1 LVDS   | 0   |           |

|          | ValEvtn           |          |     |           |

|          | RazChnp           | 1 LVDS   | 0   |           |

|          | RazChnn           |          |     |           |

|          | StartReadOut      | 1 LVTTL  | 0   |           |

|          | EndReadOut        | 1 LVTTL  | ĭ   |           |

|          | TransmitOn        | 1 LVTTL  | i   |           |

|          | Dout (out0)       | 1 LVTTL  | i   |           |

|          | RamFull           | 100      | oc  |           |

|          | TriggerExt        | 1 LVTTL  | 0   |           |

|          |                   | 1 LVTTL  | ĭ   |           |

|          | TriggerOut        | TEVITE   | '   |           |

# ASU connector

To be discussed

More I/O added to current board to follow SKiROC developments

# InSituDebugDAQ concept

On beam simplified DAQ devoted to monitor and debug a few SLABs

- chip radiation tolerance

- accurate diagnostic of unexpected behavior

- monitoring (internal probes)

- maintenance

Can run alone, eventually with no beam

compatible with machine interface or specific trigger and timing

**Dedicated Software** aimed to ease

debugging

Simultaneous DAQ operations allowed

Machine

Interface

Or

Stand alone

CCC

**Standard DAQ**

DebugDAQ Dedicated PC

**Needs DIF** (already connected to SLAB)

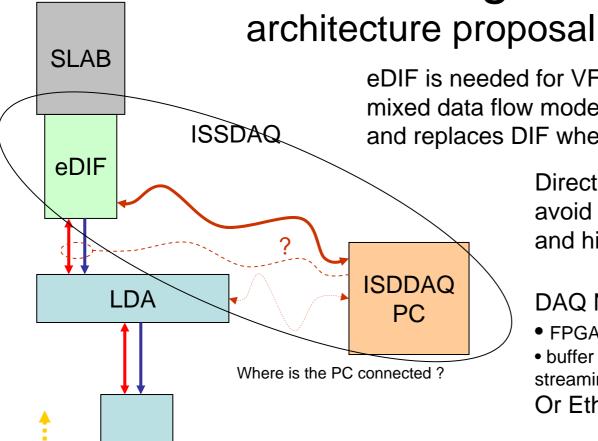

# InSituDebugDAQ

**ODR**

**TRIG**

eDIF is needed for VFE probes and mixed data flow mode (probe+DAQ) and replaces DIF when debugging

> Direct connection to LDA would avoid risky cabling operations and highest flexibility

### **DAQ NI PCI-7811R?**

- FPGA based, 160 I/O to PCI

- buffer flush mode (continuous streaming to PC)

Or Ethernet

### Software tools

Then it needs (e)xtended LDA... (CCC multiplexing) or custom interface board (serial LVDS to NI DAQ)

Light LDA for early devlopments

# ASU DAQ vs DIF (idea)

Hard/firm/software developments for ASUDAQ & ISDDAQ are Very similar as for DIF

ISDDAQ is a DIF with extended features and direct read-out

DIF is a light ASUDAQ, ASUDAQ is a DIF with extended features

- slow control of internal probes

- ADC for probe output (will be integrated into VFE ?)

- probe data read-out (additional or separate flow)

- dedicated software modules

CCC additionnal signals for users defined trigger (cosmic, no beam, ...)

Alternative Slow control access

Mechanical interface to ASU (ASUDAQ)

LDA

## eDIF proposal

first attempt architecture

## Conclusion

ASUDAQ and ISDDAQ need analogue signals of internal probing system to be connected to DIF

- eDIF concept

- architecture choice

- Combined data flow mode

### Wafer test bench being set up

- PCB specifications

- Keithley choice

- Shaper

- SILVACO simulation tools

#### **ASUDAQ**

- first developments on prototyping board

- ASU connector issue

### **ISDDAQ** architecture issue

- Internal probes

- Simultaneous DAQ

- Flexibility

## Common "all in one" prototype is being designed

- generic interfaces

- use of additional adapter board to connect to ASU, SLAB, etc...